ICT Infrastructuren

19 november 2007

David N. Jansen

1

Thema’s

•

•

•

•

•

•

Machines en machinetaal

Processen en threads

Synchronisatie en deadlock

Geheugenbeheer

Taakverdeling

Netwerken

2

Literatuur

Operating Systems: Internals and Design

Principles / William Stallings. – 5th ed. –

Upper Saddle River: Pearson, 2005

ISBN 0-13-147954-7

http://williamstallings.com/OS/OS5e.html

3

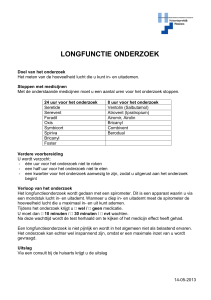

Huiswerkopgaven

• Ongeveer 1 opgave in 2 weken

• tweede afspraak om de opgaven te

bespreken: wanneer?

• Sun workstations?

4

Beoordeling

• Huiswerkopgaven + tentamen

5

Machines en machinetaal

ICT Infrastructuren

19 november 2007

David N. Jansen

6

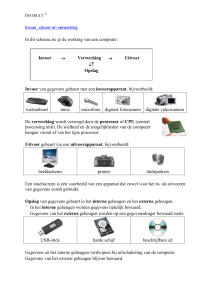

Hardware

• Welke onderdelen heeft een

computersysteem?

•

•

•

•

Processor

Hoofdgeheugen

In- en uitvoer

Bus

7

Doelen van de onderdelen

•

•

•

•

Processor: aansturen, berekenen

hoofdgeheugen: gegevens opslaan

in-/uitvoer: externe communicatie

bus: interne communicatie

8

9

bron: http://www.commodore.ca/manuals/images/c64_rev_a_250469_motherboard_schematic.gif

Opbouw van de processor

• Registers

– gegevens- en adresregisters

– vlaggen

– programmateller

– interne registers

• Arithmetisch-logische eenheid ALU

• besturingseenheid

10

8088

bron: http://faculty.etsu.edu/tarnoff/ntes2150/uproc/blck8088.gif

11

bron:http://www.icknowledge.com/trends/8086_8088B1.jpg

12

Dynamisch gedrag

• Programma’s uitvoeren:

– instructie lezen (fetch)

– instructie decoderen

– instructie uitvoeren

• bij moderne processoren: parallel

(pipelined)

13

Soorten instructies

• gegevenstransport

• berekenen

• programmaflow

14

15

bron:http://www.physics.mcmaster.ca/tech/HC908/opcode_map.gif

Opcodes

Voorbeeldprogramma

16

Interrupts

• doel: bepaalde taken uitvoeren op een

gunstig moment

• de processor onderbreekt het lopende

programma

• hij voert tussendoor de “interrupt

handler” uit

17

Soorten interrupts

•

•

•

•

programma (b.v. /0)

timer

in- of uitvoer

hardwareprobleem

18

Voordelen van interrupts

• minder lang wachten op resultaten van

in-/uitvoer

• exactere timing

19

Meerdere interrupts?

• tweede interrupt:

– negeren

– uitstellen

– onmiddellijk afhandelen

• interrupt mask, prioriteiten

20

Geheugen

• registers

• hoofdgeheugen

• secundair geheugen

21

Cache

• het secundaire geheugen is wel erg

langzaam...

• “onzichtbaar” geheugen

• kopie van een deel

22

Wat moet in de Cache

staan?

• gegevens die binnenkort gelezen

worden

• verschillende approximaties

– wat al gelezen is

– gegevens in de buurt

23

Opbouw van een cache

• snel = eenvoudig

• ingedeeld in blokken

• tag/identificatie geeft aan waar het blok

vandaan komt

24

Lezen met een cache

25

In- en uitvoer

• aansturing:

– processor-aangestuurd

– direct memory access DMA

26

Samenvatting

•

•

•

•

•

•

Hardwarestructuur

Centrale processor

Instructies (assembler)

Interrupts

Geheugen

In- en uitvoer

27