Voorbeeldexamen digitale technieken 3E – januarizittijd

1. Hoe kan je, gebruik makende van de Booleaanse algebra en/of de wetten van De

Morgan, aantonen dat je een and-or schakeling kan vervangen door een all-nor

schakeling en dat je een or-and schakeling kan vervangen door een all-nand schakeling.

2. Gegeven een waarheidstabel van 4 à 5 ingangen en twee uitgangen. (*)

Gevraagd: zoek de snelste schakeling gebruik makende van:

Karnaughkaarten

Quine-Mc Cluskey

Multiplexers

Hoe ga je uw schakeling snel houden en toch zo goedkoop mogelijk maken gebruik

makende van Karnaughkaarten.

3. Bepreek volledig de standaard TTL NAND poort met 2

ingangen.

Geef

hierbij

ook

de

definities

van

vertragingstijden. Vergelijk met andere digitale families.

4. Bespreek de pulse triggered SR latch. Waarvoor gebruikt

men deze en wat zijn de tekortkomingen?

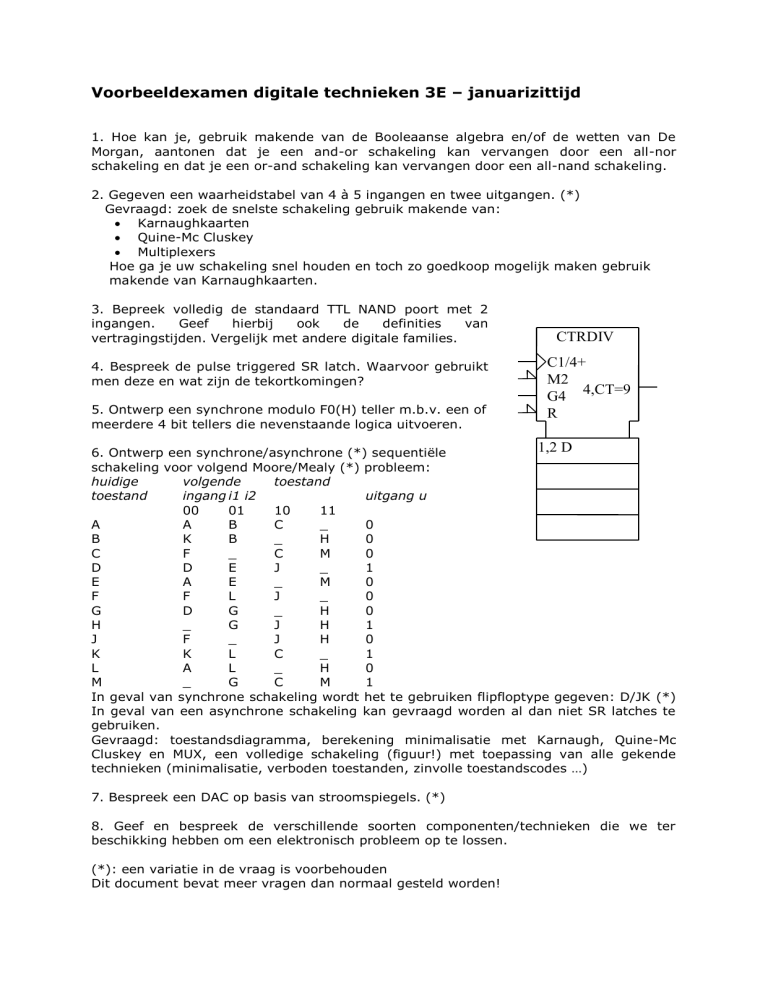

5. Ontwerp een synchrone modulo F0(H) teller m.b.v. een of

meerdere 4 bit tellers die nevenstaande logica uitvoeren.

CTRDIV

10

C1/4+

1/3/4+

M2

4,CT=9

G4

R

1,2 D

6. Ontwerp een synchrone/asynchrone (*) sequentiële

schakeling voor volgend Moore/Mealy (*) probleem:

huidige

volgende

toestand

toestand

ingang i1 i2

uitgang u

00

01

10

11

A

A

B

C

_

0

B

K

B

_

H

0

C

F

_

C

M

0

D

D

E

J

_

1

E

A

E

_

M

0

F

F

L

J

_

0

G

D

G

_

H

0

H

_

G

J

H

1

J

F

_

J

H

0

K

K

L

C

_

1

L

A

L

_

H

0

M

_

G

C

M

1

In geval van synchrone schakeling wordt het te gebruiken flipfloptype gegeven: D/JK (*)

In geval van een asynchrone schakeling kan gevraagd worden al dan niet SR latches te

gebruiken.

Gevraagd: toestandsdiagramma, berekening minimalisatie met Karnaugh, Quine-Mc

Cluskey en MUX, een volledige schakeling (figuur!) met toepassing van alle gekende

technieken (minimalisatie, verboden toestanden, zinvolle toestandscodes …)

7. Bespreek een DAC op basis van stroomspiegels. (*)

8. Geef en bespreek de verschillende soorten componenten/technieken die we ter

beschikking hebben om een elektronisch probleem op te lossen.

(*): een variatie in de vraag is voorbehouden

Dit document bevat meer vragen dan normaal gesteld worden!